### TELEFUNKEN ELECTRONIC

### LOCAL MULTIPLEX SYSTEM

T-75-45-07

**Technology: Bipolar**

#### Application:

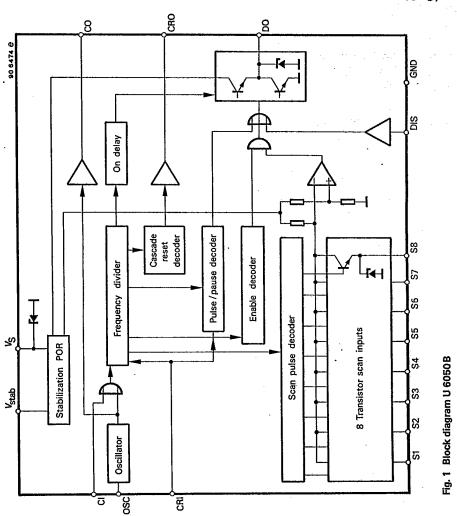

Transmitter (U 6050B) and receiver (U 6051B, U 6052B) for permanent scanning of 8 switch-positions, serial data transmission via a single data line and driving up to 8 relays.

#### Features:

- Only a single line is necessary

- Quadruple comparison of the data signal for high transmission safety

- All outputs switched off if data line is disturbed

- Short circuit detection of the integrated relay driver

- Transmitter and receiver prepared for master/slave operation (16 switches, 16 relays)

- Reduced power dissipation by pulsed driver outputs

- Transmitter data output short circuit protected

- Transmitter can be powered via data line

- Wide supply voltage range

- U 6050B: 8 relay drivers,

U 6051B: 4 relay drivers and

4 logic outputs

- Meet the demands of VDE regulation 0839

- Load dump protected

### Cases:

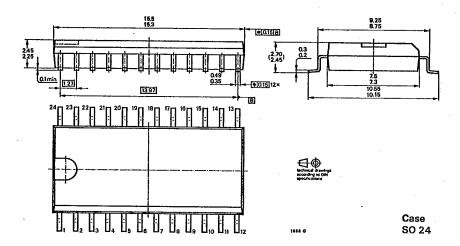

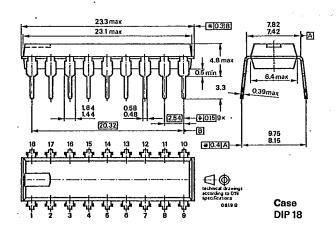

18 pin dual inline plastic (U 6050B, U 6051B, U 6052B)

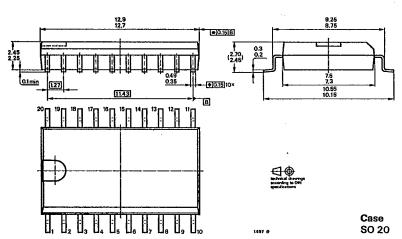

20 pin SO plastic (U 6050 B-FP)

24 pin SO plastic (U 6051 B-FP, U 6052 B-FP)

T1.2/2111.0690 E

TELEFUNKEN ELECTRONIC

T-75-45-07

TELEFUNKEN ELECTRONIC

## U 6050B · U 6051B U 6052B

T-75-45-07

119

## TELEFUNKEN ELECTRONIC

T-75-45-07

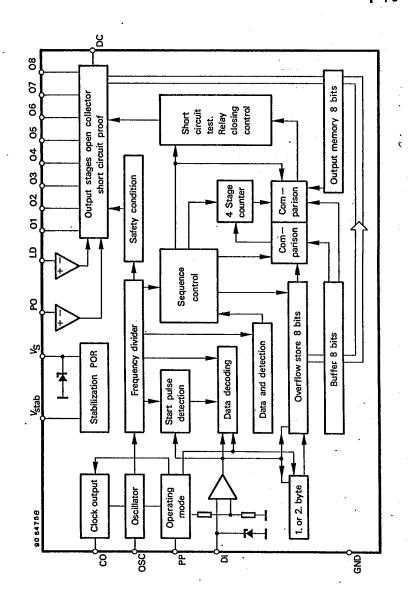

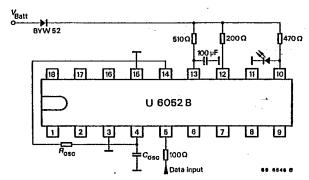

Fig. 3 Block diagram U 6052B

### TELEFUNKEN ELECTRONIC

## Functional description of transmitter and receiver

### T-75-45-07

#### 1.1 Power supply

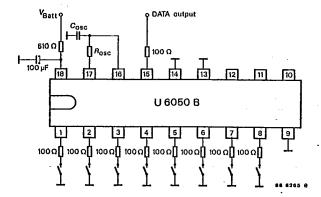

For reasons of protection against interference and surges must all circuits be equipped with an RC circuit for current limitation in the event overvoltages and for buffering in the event of voltage dips at  $V_{\rm S}$ .

Suggested dimensions:  $R_V = 510~\Omega$ ,  $C_V = 100~\mu\text{F}$ . An integrated 14 V Z-diode is located between  $V_S$  and GND in each case.

#### 1.2 Oscillator

All timing in the circuits is derived from an RC-oscillator in each case; the oscillator's charging time  $t_1$  is determined by an external resistor  $R_{\rm osc}$  and its discharge time  $t_2$  by an integrated 2 k $\Omega$  resistor. Since the tolerance and temperature sensitivity of the integrated resistor are considerably greater than those of the external resistor,  $t_1/t_2 \ge 20$  must be selected for stability reasons. The minimum value of  $R_{\rm osc}$  should not be less than 68 k $\Omega$ .

Recommended frequencies and dimensioning:

$\begin{array}{l} \textit{f}_{\rm transmitter} = ~6.4~{\rm kHz}; \textit{C}_{\rm osc} = ~1~{\rm nF}; \textit{R}_{\rm osc} = 200~{\rm k}\Omega \\ \textit{f}_{\rm receiver} = 25.6~{\rm kHz}; \textit{C}_{\rm osc} = 220~{\rm pF}; \textit{R}_{\rm osc} = 200~{\rm k}\Omega \end{array}$

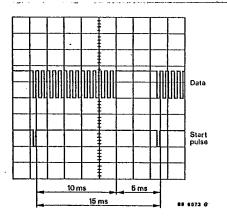

Times derived from the transmitter frequency (6.4 kHz):

| •                |                           |

|------------------|---------------------------|

| Start pulse      | : 312 µs                  |

| One bit          | ; 156 µs                  |

| Information bit  | : 156 µs                  |

| Zero bit         | : 156 us                  |

| Information unit | : 625 µs                  |

| Data word        | : 5 ms + 312 us start bit |

| Data nause       | • 9 688 ms                |

Transmission cycle : 15 ms Minimum reaction time : 60 ms

Data word master-slave: 10 ms + 312 µs start bit

Data pause master-slave : 4.688 ms Scanning pulse : 312 µs ON delay : 75 ms

#### 2. Transmitter supply via the data line

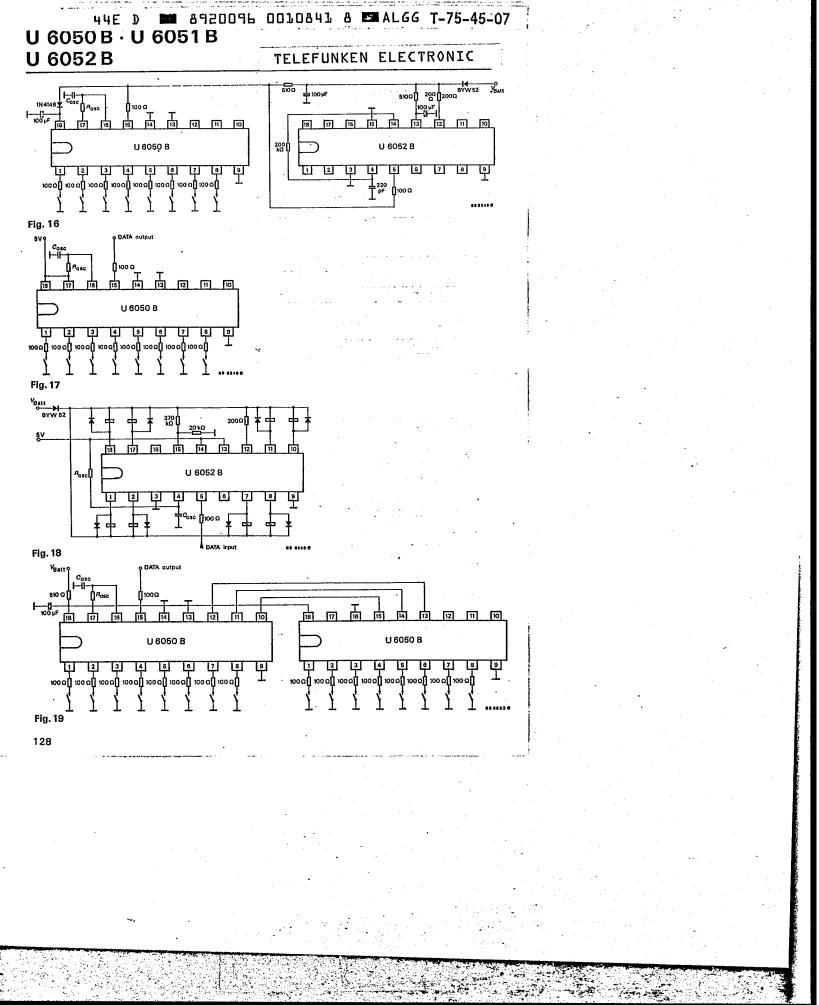

The supply line is not required if the transmitter is supplied via the data line. Refer to Fig. 16 for the wiring. It must be noted that there is greater susceptibility to faults with this wiring arrangement, but this can be eliminated by a suitable external circuit, e.g. a capacitor to ground after the reverse voltage protection diode.

Both transmitter and receiver possess an integrated 14 V Z-diode at the data output DO and data input DI for limitation of positive voltage peaks.

#### 3. 5V supply

Both the transmitters and receivers can be supplied from one stabilized, noise-free 5 V voltage source. In this case, the series resistor and the filter capacitor are not required. Pin  $V_{\rm stab}$  is also supplied by the 5 V supply.

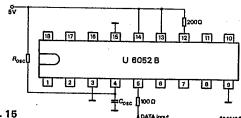

Refer to Figs. 15, 17, 18 and 20.

## 4. Functional description of the transmitter U 6050B

Eight switch or pushbutton inputs are scanned cyclically every 15 ms and the result is permanently transmitted to the receiver as a serial data word via the data line.

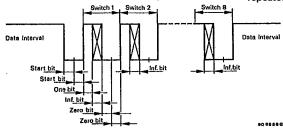

#### 4.1 Structure of the data word

A switch information unit consists of 4 parts:

1. One bit for receiver synchronization

2. Information bit with "High" = switch open

"Low" = switch closed

3. Zero bit

4. Zero bit

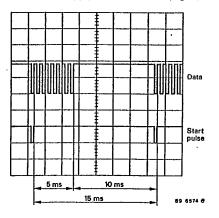

The data word consists of 2 start bits and 8 information units. For a transmitter frequency of 6.4 kHz, the data word length is 5 ms plus the start pulse, followed by a 10 ms long data interval. The data interval has high potential. When the supply voltage is applied, data transmission is constantly repeated in accordance with this pattern (Fig. 4).

### TELEFUNKEN ELECTRONIC

T-75-45-07

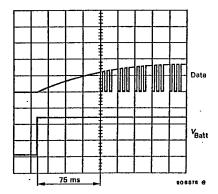

#### 4.2 ON delay and POR

After the supply voltage  $V_{\rm batt}$  is applied to the transmitter, a POWER-ON-RESET pulse (POR) is generated internally which sets the logic of the U 6050B to a basic condition. This also applies to the other circuits. The data output is blocked for approx. 75 ms so that the supply capacitor can be charged up when  $V_{\rm batt}$  is switched on in the case of transmitter supply via the data line (Fig. 5).

#### 4.3 Switch input scanning

For reliable detection of the switch condition, a certain minimum current must flow through the switch contact so that soiling and moisture cannot lead to misinterpretations.

Avalue of 2 mA was planned for the contact current. To reduce the overall current consumption of the transmitter, the switches are supplied cyclically with the contact current, so that the power consumption is rediced from the maximum of 16 mA to 0.33 mA owing to the duty factor of 2.5/15.

The voltage drop across the inputs caused by the current is compared with a reference voltage of 2.5 V; if the potential is less than 2.5 V during the scan pulse, the switch is closed, while the switch is open if the potential is greater than 2.5 V. The leakage resistance of the switching contact can thus be approx. 2.5 k $\Omega$  if a protective resistor of 100  $\Omega$  is provided. Protective resistors for limitation of interference voltage peaks at the inputs are long. In a noise-free environment, the protective resistors at the switch inputs can be omitted. The input posses an integrated 14 V Z-diode.

Fig. 4

Fig. 5

Fig. 6

## U 6050 B · U 6051 B U 6052 B <sub>T-75-45-07</sub>

TELEFUNKEN ELECTRONIC

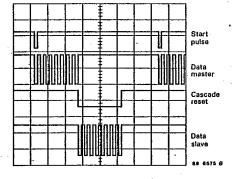

Fig. 7

#### 4.4 Cascading (master-slave operation)

Scanning of up to 16 switches or pushbuttons is possible by connecting together two transmitters. The connection between master and slave is shown in Fig. 19. The data output DO of the slave is connected with the data input DIS of the master; the two data signals are combined with each other there and are available at the data output DO of the master (Fig. 6 and 7).

The master transmits the start bit and the first eight information units; in this time, the frequency divider of the slave is disabled by the master's

cascade reset. After the last master information unit, the slave frequency divider is enabled so that the slave scanning cycle and slave data transmission can be performed. In master-slave operation, the data word consists of the start bit and 16 information units (10 ms); the data interval is 5 ms. The clock output CO of the master is connected with the clock input of the slave CI so that the time sequences of both circuits are synchronous. The voltage supply can be realized with a common series resistor and a common filter capacitor.

Operation with 5 V is possible, refer to Fig. 20.

#### 4.5 Data output DO

The data output is a push-pull output which is short-circuit proof both with respect to ground and  $V_{\rm batt}$ . The current limiter is set to approx. 30 mA in both cases. A 14 V Z-diode is located between DO and GND to clip interference voltages. For this reason, an external series resistor of 100  $\Omega$  is also required to limit the current in the Z-diode (Fig. 8).

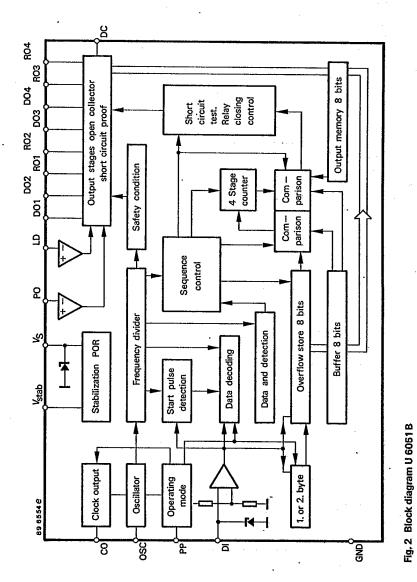

# 5. Functional description: receiver U 6050B/U 6051B

Reception of the information arriving from the transmitter, decoding of the data word, i.e. recognition of the switch conditions and activation of the corresponding relay drivers after a data check.

Fig. 8

#### TELEFUNKEN ELECTRONIC

#### 5.1 Data decoding

If a negative edge appears at the data input, the receiver checks wether a start pulse or a fault is present by measuring the duration of the pulse. (A minimum time must be observed). If there is a fault, the receiver waits for the next negative edge.

If it recognises a start pulse, it checks wether an information unit with 8 bits is following and stores this in an 8-bit overflow store. The arriving data are ignored if there is no 8-bit string owing to a fault or a synchronism. The receiver is synchronized by each one bit; scanning of the information takes place in the middle of the information bit. In order to make scanning sufficiently precise, the oscillator frequency of the receiver was selected to be four times as large as that of the transmitter. The deviation of the receiver frequency to the four-fold transmitter frequency may be up to  $\pm\,15\,\%$  while still guaranteeing reliable data recognition.

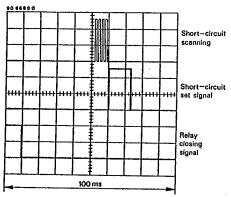

#### 5.2 Data check

The data read into the 8-bit overflow store are compared with the contents of the buffer. If they are identical, a 4-stage counter is incremented by one stage: if they are not identical, the counter is reset. The new data combination is transferred to the buffer after each comparison, irrespective of the result.

After coincidence has been established four times, the contents of the buffer are compared with the contents of the output memory. If both are identical, the 4-stage counter is reset. However, since nothing has changed with respect to the switch position, the information from the buffer is not transferred to the output memory. This is important if the relay drivers are in clocked condition. However, if the contents of the two

### T-75-45-07

memories differ, the switch position must have changed in the meantime, and the following process occurs:

a. Relays are operated statically.

The information is transferred from the buffer to the output memory and the corresponding relay outputs are activated. An individual short-circuit test takes place for 10 ms after approx. 35 ms. If a short-circuit is detected, the respective output is disabled until a new POR occurs.

Relays are clocked.

After transfer to the output memory, the corresponding relay outputs are activated statically for approx. 120 ms; in this time, the short-circuit test described in a) is performed. The relay outputs are then clocked with the oscillator frequency.

Since the period of a data transmission is 15 ms, this results in a minimum delay time or debouncing time of  $4\cdot15$  ms = 60 ms for detection of a change in switch position. Faults on the data line and switch bouncing may lead to an extension of the delay time.

#### 5.3 Safety position of the relay drivers

If no data reach the receiver any longer owing to a break in the data line or a short-circuit to ground or  $V_{\rm S}$ , then all relay drivers are disabled after approx. 50 ms. It is possible to visually indicate the malfunction by permanently wiring a transmitter input to ground and connecting the corresponding relay output in accordance with Fig. 9. This applies only to static operation or when using a digital output of U 6051B.

Fig. 9

## TELEFUNKEN ELECTRONIC

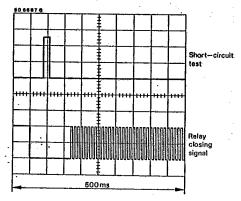

### 5.4 Short circuit detection of the outputs

Approx. 35 ms after a new data transfer operation to the output memory, a comparator measures the collector voltage of every active output transistor for 10 ms. If the saturation voltage exceeds the value of 2 V, this is interpreted as a short-circuit. The delay of 35 ms also permits connection of a 1.2 W lamp: the high initial current after switching on has died away by then and cannot lead to erroneous tripping of the short-circuit detection circuit. Measurement is not performed statically so that faults cannot simulate a short-circuit; in practice, this means that each active output is measured four times in the period of 10 ms (Fig. 10). Experience shows that fault pulses in a motor

Fig. 10

#### 5.5 Output clocking

Clocking of the relay outputs leads to a reduction in the power dissipation of the circuit and the overall equipment. The operating modes "output clocking",  $PO = V_S$  or "static activation", PO = GND, can be selected by the input PO.

After a new information transfer operation to the output memory, the relay outputs to be activated are statically activated for a period of approx. 120 ms. The above-described short-circuit test also takes place in this time and the outputs are then clocked with a frequency of 25.6 kHz, i.e. with the oscillator's fundamental frequency. Refer to Fig. 11.

Clocking of the outputs is switched off in the event of a supply voltage of  $V_{\rm Batt} \le 10 \text{ V}$ : clocking is then switched back on again for  $V_{\rm Batt} \ge 11 \text{ V}$ . Detection of these voltage thresholds is also performed by the

### T-75-45-07

vehicle are shorter than 2 ms. The corresponding transistor is rendered reverse-biased only if the collector voltage is greater than 2 V for longer than 10 ms owing to a short circuit; this condition is then stored and can be cancelled again only by a POR. A short-circuit which occurs at a later time can be detected only when a new switch combination is set and a new short-circuit test takes place. However, an active transistor will be destroyed by a subsequent short-circuit to  $V_{\rm batt}$ . If a transistor is reverse-biased owing to a short-circuit, the remaining functions of the receiver are not impaired by this.

Fig. 11

input PO if this is provided with a voltage divider. The reference voltage for "clocking off" is around 2 V/2.27 V. With an external voltage divider of 150 kΩ/39 kΩ, this corresponds to a response threshold of  $V_{\text{Batt}} = 10 \text{ V/11 V, refer to Fig. 12.}$ Clocking of the relays over the whole supply voltage range requires a separate free-wheeling diode for each relay which can also block the required interference voltages, e.g. BAV 21. Since negative interference voltages can reach the collectors of the output transistors with low resistance via these free-wheeling diodes, a high-blocking capability reverse voltage protection diode, e.g. a BYW 52, must be connected in the supply line, because these interference voltages would otherwise lead to destruction of the transistors.

T-75-45-07

### TELEFUNKEN ELECTRONIC

#### 5.6 Driver control DC

A relatively high current is required for activation of all eight output transistors. This would lead to a large voltage drop across  $R_{\rm v}$  if this current were taken from the internal supply voltage. For this reason, the activation current of the relay drivers is routed via a separate terminal DC.

It was not possible to use Darlington transistors with low base currents because the aim was a maximum saturation voltage of  $V_{\rm CEsat} \le 0.5$  for  $I_{\rm C}=150$  mA. In the event of a fault, the potential of DC is connected to ground via a Darlington transistor. Recommended series resistance for DC:  $R_{\rm DC}=200~\Omega$ .

#### 5.7 Surge immunity, input LD

The IC supply is protected by an external RC circuit and an integrated 14 V Z-diode.

Since the output transistors cannot withstand long positive voltage peaks and the load dump pulse in reverse-biased condition without damage, they are switched to forward-biased condition in the event of a fault. The output transistors are dimensioned so that they can cope with the current produced through an 80  $\Omega$  winding as a result of the load dump pulse.

At the same time, the potential at DC is also connected to ground via a Darlington transistor. The outputs are gated via output transistors reconnected to form Darlington transistors.

If a lamp is connected, the current may become so high in the event of a load dump in conjunction with the initial resistance of the lamp that the output transistor and lamp may be destroyed.

The response threshold is defined with an external voltage divider at the input LD. The reference voltage for overvoltages is around 2 V/1.5 V, this corresponding to a  $V_{batt}$  response voltage of approx. 30 V and a hysteresis of approx. 9 V.

In the event of positive overvoltages, every short-circuit scan is also suppressed.

#### 5.8 Cascading (master-slave operation)

Determination of master or slave is performed by wiring the programming input PP at the U 6052B:

Master: PP to V<sub>S</sub>

Alone: PP open

Slave: PP to GND

In "master" mode, the oscillator is connected with  $R_{\rm osc}$  and  $C_{\rm osc}$  and the clock output CO is active. If the receiver is operated alone, CO is disabled. In "slave" mode, the oscillator is blocked internally and must be activated by the clock output of the master; the slave's clock output is disabled.

The master recognises the start bit and decodes the first eight information bits. The slave also recognises the start bit, but decodes the second eight information bits.

Except for the synchronous clock control, the functions for master and slave are executed independently. The wiring and configuration in master-slave mode is shown in Figs. 21 and 22.

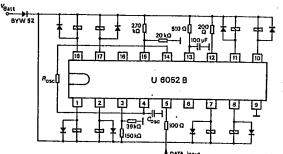

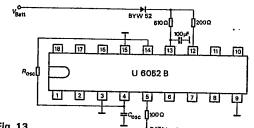

# 5.9 Activation of 8 logic outputs with U 6052 B

Instead of being used for activation of relays, the 8 outputs can also be used for activation of a downstream digital circuit. The outputs must then not be clocked: PO = GND.

The outputs must also not be gated by overvoltages, i.e. LD = GND. Refer to Fig. 13. The outputs are npn open collector transistors and are capable of switching 200 mA and blocking up to 25 V. However, it must be ensured that no overvoltages and no load dump can reach the output transistors in this circuit configuration.

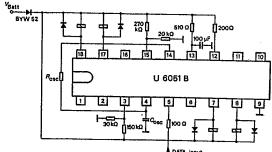

#### 6. Modified receiver U 6051B

The U 6051B is a mask version of U 6052B possessing 4 relay outputs and 4 logic outputs, refer to Figs. 14 and 22.

The relay outputs correspond to those of U 6052 B. The logic outputs are connected by means of an aluminium mask to form an npn Darlington open collector with integrated 22 V Z-diode. Clocking and gating by overvoltages are not possible. The saturation voltage is less than 1 V for  $I_{\rm C}=20$  mA. Overvoltages may reach the logic outputs only with a series resistance of 1 k $\Omega$ .

TELEFUNKEN ELECTRONIC

T-75-45-07

Fig. 12

Fig. 13

Fig. 14

Fig. 15

## 44E D 🔤 8920096 0010843 1 📼 ALGG

## U 6050 B · U 6051 B U 6052 B

### TELEFUNKEN ELECTRONIC

### Pin configuration (U 6050B)

T-75-45-07

| Pin | Function |

|-----|----------|

|     |          |

1...8 Switch inputs S1...S8

(2...9)

9 (10) Ground GND

10 (11) Data input slave DIS

11 (13) Cascading reset output CRO

12 (14) Clock output for cascading CO

13 (15) Clock input for cascading Cl

14 (16) Cascading reset input CRI

15 (17) Data output DO

16 (18) RC-oscillator input OSC

17 (19) Stabilized voltage V<sub>stab</sub>

18 (20) Supply voltage V<sub>S</sub>

(1, 12) N.C.

### Pin configuration (U 6051 B)

## Pin Function

( 1) Ground GND

1 (2) Logic output DO1

2 (3) Logic output DO2

3 (5) Program pin pulsed output PO

4 ( 6) RC-oscillator input OSC

5 (7) Data input Di

6 (8) Program pin (tristate) PP

7 (10) Relay output RO1

8 (11) Relay output RO2

9 (12) Ground GND

(13) Ground GND

10 (14) Logic output D03

11 (15) Logic output DO4

12 (17) Driver control DC

13 (18) Supply voltage V<sub>S</sub>

14 (19) Stabilized voltage V<sub>stab</sub>

15 (20) Load dump detection LD

16 (21) Clock output for cascading CO

17 (22) Relay output RO3

18 (23) Relay output 04

(24) Ground GND

(4, 9, 16) N. C.

### Pin configuration (U 6052B)

#### Pin Function

(1) Ground GND

1 (2) Relay output 01

2 (3) Relay output Q2

3 (5) Program pin pulsed output PO

4 ( 6) RC-oscillator input OSC

5 (7) Data input DI

6 (8) Program pin (tristate) PP

7 (10) Relay output 03

8 (1.1) Relay output 04

9 (12) Ground GND

(13) Ground GND

10 (14) Relay output 05

11 (15) Relay output 06

12 (17) Driver control DC

13 (18) Supply voltage V<sub>S</sub>

14 (19) Stabilized voltage V<sub>stab</sub>

15 (20) Load dump detection LD

16 (21) Clock output for cascading CO 17 (22) Relay output 07

18 (23) Relay output 08

(24) Ground GND

(4, 9, 16) N. C.

Numbers in brackets apply to SO package

44E D - 8920096 0010844 3 - ALGG

# U 6050 B · U 6051 B U 6052 B

| TELEFUNKEN ELECTRONIC                                                                                           |                 |                                         | U 60 |           |          |            |

|-----------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------|------|-----------|----------|------------|

| U 6050B Transmitter (with re-                                                                                   | commen          | ded circuitry)                          |      | Τ.        | -75-45-  | 07         |

| Absolute maximum ratings                                                                                        |                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      |           |          |            |

| Supply voltage (static)                                                                                         |                 |                                         |      |           |          |            |

| no operation 60 s                                                                                               |                 | $V_{\rm S}$                             |      | 25        |          | . V        |

| Ambient temperature range                                                                                       |                 | $T_{amb}$                               |      | -40+85    |          | °C         |

| Storage temperature range                                                                                       |                 | $T_{ m stg}$                            |      | -55+12    | 5        | °C         |

| Junction temperature                                                                                            |                 | $\tau_{i}$                              |      | 150       |          | _ ი        |

| Power dissipation T <sub>amb</sub> = 85 °C                                                                      |                 | P <sub>tot</sub>                        |      | 810       |          | mW         |

| Maximum thermal resistance                                                                                      |                 |                                         |      |           |          | -          |

|                                                                                                                 | DIP 18<br>SO 20 | R <sub>thJA</sub><br>R <sub>thJA</sub>  |      | 80<br>100 | <u>.</u> | K/W<br>K/W |

| Electrical characteristics                                                                                      |                 |                                         | Min, | Тур.      | Max.     |            |

| $V_{\text{Batt}} = 13.5 \text{ V}, T_{\text{amb}} = 25 \text{ °C}, \text{ re}$<br>Transmitter operated with red |                 |                                         | 8)   | • ••      | :        |            |

| Supply voltage                                                                                                  |                 | $V_{Batt}$                              | 6    |           | 16       | V.         |

| 5 V supply (without $R_{ m V}$ , $C_{ m V}$ )                                                                   |                 | V <sub>S</sub> , V <sub>Stab</sub>      | 4.3  |           | 6        | ٧          |

| Stabilized voltage                                                                                              |                 | $V_{Stab}$                              |      | 5.2       |          | v          |

| Protection resistor<br>Filter capacitor                                                                         |                 | R <sub>∨</sub><br>C <sub>∨</sub>        | 510  | 100       |          | Ω<br>μF    |

| POR threshold                                                                                                   |                 | <b>V</b> s                              | 3.0  |           | 4.2      | v          |

| Current consumption                                                                                             |                 | l <sub>s</sub>                          |      | 1.5       |          | mA         |

| Internal clamping                                                                                               |                 | $v_{z}$                                 |      | 14.3      |          | . V        |

| Switch input S1S8                                                                                               |                 |                                         |      |           |          |            |

| Scan current                                                                                                    |                 |                                         |      |           |          |            |

| $(V_{\rm S1S8}=0\ V)$                                                                                           |                 | - I <sub>S1S8</sub>                     |      | 2         |          | mA         |

| Leakage resistance                                                                                              |                 | R <sub>S1S8</sub>                       | 1.8  |           | 3        | kΩ.        |

| Internal reference                                                                                              |                 | $V_{Ref}$                               |      | 2.5       |          | · • V      |

| Recommended protection resi                                                                                     | istor           | R <sub>S1S8</sub>                       |      | 100       | -        | Ω.         |

| Internal clamping                                                                                               |                 | V <sub>Z1Z8</sub>                       |      | . 14.3    |          | V          |

| Oscillator input OSC                                                                                            |                 |                                         |      |           |          |            |

| Internal discharge resistor                                                                                     |                 | R <sub>Dis</sub>                        | 1.6  | 2.0       | 2.4      | kΩ         |

| Lower threshold                                                                                                 |                 | V <sub>osc</sub>                        |      | 1.1       |          | ٧          |

| Upper threshold                                                                                                 |                 | V <sub>osc</sub>                        |      | 3.3       | •        | ٧          |

| Input current<br>(V <sub>osc</sub> = 0 V)                                                                       |                 | -l <sub>osc</sub>                       |      |           | . 1      | μА         |

| Oscillator frequency                                                                                            |                 | fosc                                    | 1.0  | 6.4       | 20.0     | kHz        |

44E D 💌 8920096 0010845 5 🛤 ALGG

U 6050 B · U 6051 B U 6052 B

T-75-45-07

TELEFUNKEN ELECTRONIC

| O 0002 D                                                                   | TELLI ORKER ELLCINORA           |   |      |                       |      |            |

|----------------------------------------------------------------------------|---------------------------------|---|------|-----------------------|------|------------|

| •                                                                          |                                 | • | Min. | Тур.                  | Max. |            |

| Clock input Cl                                                             |                                 |   |      |                       |      | : ' •      |

| Internal serial resistor                                                   | R <sub>CI1</sub>                |   |      | 2                     |      | kΩ         |

| Internal pull down resistor                                                | R <sub>CI2</sub>                |   |      | 20                    |      | kΩ         |

| Threshold                                                                  | V <sub>CI</sub>                 | - |      | 0.6                   |      | V          |

| Clock output CO                                                            |                                 |   |      | •                     |      |            |

| Output current "high" (V <sub>CO</sub> = 0 V)                              | -/ <sub>co</sub>                |   |      |                       | 150  | μA         |

| Saturation voltage "low"                                                   | V <sub>co</sub>                 |   |      |                       | 1    | V          |

| Cascade reset input CRI                                                    |                                 |   |      |                       |      |            |

| Internal serial resistor                                                   | R <sub>CRI1</sub>               |   |      | 2                     |      | kΩ         |

| Internal pull down resistor                                                | R <sub>CRI2</sub>               |   |      | 20                    |      | kΩ         |

| Threshold $V_{CRI} = 0 \text{ V: normal operation } V_{CRI} = V_S : reset$ | V <sub>CRI</sub>                |   |      | 0.6                   |      | <b>v</b>   |

| Cascade reset output CRO Output current "high"                             |                                 |   |      |                       |      | 1.<br>     |

| $(V_{CRO} = 0 \text{ V})$                                                  | -/ <sub>CRO</sub>               |   |      | •                     | 150  | μ <b>Α</b> |

| Saturation voltage "low"                                                   | V <sub>CRO</sub>                |   |      |                       | 1    | v          |

| Data output DO                                                             |                                 |   |      |                       |      |            |

| Saturation voltage "low" (20 mA)                                           | $V_{DO}$                        |   |      |                       | 1.5  | v          |

| Saturation voltage "high" (20 mA)                                          | V <sub>DO</sub> /V <sub>S</sub> |   |      |                       | 2.4  | • v        |

| Current limitation                                                         |                                 |   |      |                       |      | ٠          |

| $(V_{DO} = 0 \text{ V})$ $(V_{DO} = V_{Batt})$                             | -/ <sub>DO</sub>                |   |      | 30<br>30              | . •  | mA<br>mA   |

| Internal clamping                                                          | $V_{z}$                         |   |      | 14.3                  |      | ٧          |

| External protection resistor                                               | $R_{DO}$                        |   | 100  |                       |      | Ω          |

| Data input - slave DIS                                                     |                                 |   |      | -                     |      |            |

| internal pull-up resistor                                                  | R <sub>DIS</sub>                |   |      | 100                   |      | kΩ         |

| Detection threshold                                                        | $v_{\text{DIS}}$                |   | -    | 0.66 ⋅ V <sub>s</sub> |      | ٧          |

| TELE | 7 F I | 1 N I | 75  | N  |      | T D | $\wedge$ N | TC |

|------|-------|-------|-----|----|------|-----|------------|----|

|      | ., L  | ,,,,, | \ L | 14 | <br> | 11/ | VII        | 1  |

| U 6051B, U 6052B Receiver (with                                                                                   | recommended circ                   | cuitry)  | T-7     | 5-45- | -07        |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------|----------|---------|-------|------------|

| Absolute maximum ratings                                                                                          |                                    |          | ***     |       |            |

| Supply voltage (static) no operation 60 s                                                                         | V <sub>s</sub>                     |          | 25      |       | . <b>v</b> |

| Ambient temperature range                                                                                         | T <sub>amb</sub>                   |          | -40+ 85 |       | °C         |

| Storage temperature range                                                                                         | $T_{ m stg}$                       |          | -55+125 |       | °C         |

| Junction temperature                                                                                              | $\tau_{\rm j}$                     |          | 125     |       | · °C       |

| Power dissipation $(T_{emb} = 85  ^{\circ}\text{C})$                                                              | $P_{\mathrm{tot}}$                 |          | 860     |       | mW         |

| Maximum thermal resistance                                                                                        |                                    |          |         |       |            |

| Junction ambient                                                                                                  | RthJA                              |          | 75      |       | K/W        |

| Electrical characteristics                                                                                        |                                    | Min.     | Тур.    | Max.  |            |

| $V_{\rm Batt} = 13.5 \text{ V}$ , $T_{\rm amb} = 25 ^{\circ}\text{C}$ , refere<br>Receiver operated with recommen | ence GND<br>aded circuitry         |          | •       |       |            |

| Supply voltage                                                                                                    | <b>V</b> <sub>Batt</sub>           | 6        |         | 16    | V          |

| 5 V supply (without $R_{ m V}$ , $C_{ m V}$ )                                                                     | V <sub>S</sub> , V <sub>Stab</sub> | 4.3      |         | 6     | v          |

| Stabilized voltage                                                                                                | V <sub>Stab</sub>                  |          | 5.2     |       | . <b>V</b> |

| Protection resistor<br>Filter capacitor                                                                           | R <sub>V</sub><br>C <sub>V</sub>   | 510      | 100     | •     | Ω<br>μF    |

| POR threshold                                                                                                     | V <sub>s</sub>                     | 3.0      |         | 4.2   | V          |

| Cutrent consumption (all outputs off)                                                                             | l <sub>s</sub>                     |          | 2.0     |       | mA         |

| Internal clamping                                                                                                 | V <sub>z</sub>                     |          | 14.3    |       | . V        |

| Relay output 0108 (U 6052B); R                                                                                    | 01R04 (U6051B)                     | <b>.</b> |         |       |            |

| Saturation voltage (I <sub>0</sub> = 150 mA)                                                                      | $v_{\rm o}$                        |          |         | 0.5   | v          |

| Relay coil resistance                                                                                             | Ro                                 | 80       |         | 0.0   | . Ω        |

| Collector current (normal operation)                                                                              | l <sub>o</sub>                     | •        |         | 200   | mA         |

| Collector pulse current (load dump)                                                                               | l <sub>OP</sub>                    |          |         | 1.5   | Ą          |

| Threshold short circuit detection (output activated)                                                              | v <sub>os</sub>                    |          | 2       |       | v          |

44E D 8920096 0010847 9 ALGG

U 6050 B · U 6051 B U 6052 B

T-75-45-07

TELEFUNKEN ELECTRONIC

|                                                   | *. *.                              | Min. | Typ.                                           | Max.        |       |

|---------------------------------------------------|------------------------------------|------|------------------------------------------------|-------------|-------|

| Logic outputs D01D04 (U 6051B)                    |                                    |      | 1.1.1.1.1.1                                    | 5° 4.       |       |

| Saturation voltage                                |                                    |      |                                                |             |       |

| $(I_0 = 20 \text{ mA})$                           | v <sub>o</sub>                     |      | . •                                            | 1.0         | · V   |

| Collector current                                 | l <sub>o</sub>                     |      |                                                | 5 <b>30</b> | mΑ    |

| Internal clamping                                 | $V_{Z}$                            | •    | 22                                             | 1000        | · V   |

| Threshold short circuit detection                 | Vos                                |      | 2                                              |             |       |

| Oscillator input OSC                              |                                    |      |                                                |             | ٠.    |

| Internal discharge resistor                       | R <sub>DIS</sub>                   | 1.6  | 2.0                                            | 2.4         | kΩ    |

| Lower threshold                                   | Vosc                               |      | 1.1                                            |             | ٧     |

| Upper threshold                                   | v <sub>osc</sub>                   |      | 3.3                                            |             | · ·   |

| Input current                                     |                                    |      |                                                | er jost da  | + 1 . |

| $(V_{OSC} = 0 \text{ V})$                         | -I <sub>osc</sub>                  |      |                                                | 1           | μA    |

| Frequency                                         | f <sub>osc</sub>                   | 1.0  | 25.6                                           | 50.0        | kHz   |

| Data input DI                                     |                                    |      |                                                |             | S :   |

| Threshold                                         | $V_{DI}$                           |      | 0.5 · V <sub>S</sub>                           |             | \     |

| Internal pull down resistor                       | $R_{DI}$                           |      | 100                                            |             | kΩ    |

| Internal clamping                                 | $v_z$                              |      | 14                                             |             | V     |

| Input current                                     |                                    |      |                                                | . ,         |       |

| $(V_{DI} = O \; V) \qquad .$                      | -/ <sub>Di</sub>                   |      |                                                | 1           | μA    |

| External protection resistor                      | R                                  | 100  |                                                |             | . Ω   |

| Programm pin PP                                   |                                    |      |                                                |             |       |

| Lower threshold                                   | V <sub>PP</sub>                    |      | 0.13 · V <sub>S</sub>                          |             | V     |

| Upper threshold<br>Pin PP open                    | V <sub>PP</sub><br>V <sub>PP</sub> |      | 0.50 · V <sub>s</sub><br>0.27 · V <sub>s</sub> |             | ٠,٧   |

| Input current                                     | <b>▼</b> PP                        |      | 0.27 Vs                                        |             | •     |

| $(\dot{V_{PP}} = 0 \text{ V})$                    | - <i>I</i> <sub>PP</sub>           |      | 30                                             |             | μΔ    |

| $(V_{PP}=V_S)$                                    | I <sub>PP</sub>                    |      | 50                                             |             | μΔ    |

| Pin PP: operation mode                            |                                    |      |                                                |             |       |

| open single<br>GND slave<br>V <sub>S</sub> master |                                    |      |                                                |             |       |

| Clock output CO (activated only in m              | aster mode)                        |      |                                                |             |       |

| Output current "high"                             |                                    |      |                                                |             |       |

| $(V_{CO} = 0 \text{ V})$                          | - <i>I</i> <sub>10</sub>           |      | •                                              | 150         | μΑ    |

| Saturation voltage "low"                          | $V_{10}$                           |      |                                                | 1           | ٧     |

| Separate driver control DC                        |                                    |      |                                                |             |       |

| External protection resistor                      | A <sub>DC</sub>                    | 200  |                                                |             | , Ω   |

| Control current                                   | I <sub>DC</sub>                    |      |                                                | 40          | mA    |

| Load dump reduction voltage                       | V <sub>DC</sub>                    |      |                                                | 2           | ٧     |

## 44E D 🔤 8920096 0010848 0 🖼 ALGG

TELEFUNKEN ELECTRONIC

U 6050 B · U 6051 B U 6052 B

| Lood down data attacks                                                                                                      |                    | Min. | Тур.     | Max.   |     |  |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------|------|----------|--------|-----|--|

| Load dump detection LD                                                                                                      | T-75-45-07         |      |          |        |     |  |

| Recommended voltage divider 2                                                                                               | 70/20 kΩ           |      | (-/:     | J=40=U | ,   |  |

| Load dump threshold                                                                                                         | $V_{LD}$           |      | 2.1/1.4  |        | . v |  |

| Load dump threshold                                                                                                         | $V_{Batt}$         |      | 30/21    |        | V   |  |

| Internal clamping                                                                                                           | $V_{z}$            |      | 7        |        | V   |  |

| Input current (V <sub>LD</sub> = 0 V)                                                                                       | -/ <sub>LD</sub>   |      |          | 1      | μΑ  |  |

| Program pin Pulsed Output PO                                                                                                |                    |      |          |        |     |  |

| Recommended voltage divider 15                                                                                              | 50/39 kΩ           |      |          |        |     |  |

| Threshold pulsed output off                                                                                                 | V <sub>PO</sub>    |      | 2.0/2.27 |        | v   |  |

| Threshold pulsed output off                                                                                                 | $V_{Batt}$         |      | 10/11    |        | v   |  |

| Internal clamping                                                                                                           | $V_{z}$            | · -  | 7        |        | · V |  |

| Input current (V <sub>PO</sub> = 0 V)                                                                                       | I <sub>PO</sub>    |      |          | 1      | μA  |  |

| Input current $(V_{PO} = V_S)$                                                                                              | I <sub>PO</sub>    |      |          | 1      | μA. |  |

| $V_{PP} = 0 \text{ V}$ : static output<br>$V_{PP} = V_{S}$ : pulsed output                                                  |                    |      | • •      |        |     |  |

| IC power consumption                                                                                                        |                    |      |          |        |     |  |

| $(V_{\rm Batt} = 16 \text{ V}, V_{\rm sat} = 0.5 \text{ V},$<br>eight 80 Ω relays activated,<br>$R_{\rm DC} = 200 \Omega$ ) |                    |      |          |        |     |  |

| U 6052 B static                                                                                                             | $P_{\mathrm{tot}}$ |      | 1130     |        | mW. |  |

| U 6052B pulsed                                                                                                              | P <sub>tot</sub>   |      | 500      |        | mW  |  |

| U 6051 B static                                                                                                             | P <sub>tot</sub>   |      | 750      |        | mW  |  |

| U 6051 B pulsed                                                                                                             | $P_{tot}$          |      | 475      |        | mW  |  |

## TELEFUNKEN ELECTRONIC

Dimensions in mm

T-75-45-07

44E D 8920096 0010850 9 88ALGG

U 6050 B · U 6051 B

TELEFUNKEN ELECTRONIC

U 6052B

Dimensions in mm

T-75-45-07